# **TELEDYNE** SEMICONDUCTOR

The Analog Signal Processing Company "

**TSC8703 TSC8704**

# **BINARY OUTPUT ADCs**

T.51.10.01

- High Accuracy Up to 12 Bit Resolution With <±1/2 LSB Error

- Monotonic Performance No Missing Codes

- Monolithic CMOS Construction Gives Low Power Dissipation — 20 mW Typical

- **■** Contains All Required Active Elements Needs only Passive Support Components, Reference Voltage and Dual Power Supply

- High Stability Over Full Temperature Range

- Gain Temperature Coefficient Typically <25 ppm/°C

- Zero Drift Typically <30  $\mu$ V/°C

- Differential Non-Linearity Drift Typically <25 ppm/°C

- **Latched Parallel Binary Outputs**

- LPTTL, 74LS, CMOS Compatible Outputs and Con-

- Strobed or Free Running Conversion

- Infinite Input Range Any Positive Voltage Can Be Applied Via a Scaling Resistor

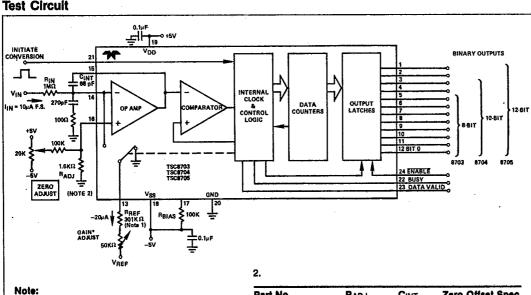

### **Test Circuit**

1. Any VREF greater than -1 V can be used.

RREF = VREF -20 µA

For example with VREF = -5 V, RREF = 250 k.

| Part No.     | RADJ   | CINT  | Zero Offset Spec |

|--------------|--------|-------|------------------|

| TSC8703      | 1.6 kΩ | 68 pF | ±80 mV           |

| TSC8703      | 1.0 kΩ | 33 pF | ±50 mV           |

| TSC8704/8705 | 1.0 kΩ | 68 pF | ±50 mV           |

### **BINARY OUTPUT ADCs**

T-51-10-01

### **GENERAL DESCRIPTION**

The TSC8703/8704/8705 are 8/10/12 bit monolithic CMOS analog-to-digital converters. Fully self-contained in a single 24-pin dual in-line package, each converter requires only passive support components, reference and power supplies.

Conversion is performed by an incremental charge balancing technique which has inherently high accuracy, linearity and noise immunity. An amplifier integrates the sum of the unknown analog current and pulses of a reference current, and the number of pulses (charge increments) needed to maintain the amplifier summing junction near zero is counted. At the end of conversion the total count is latched into the digital outputs as an 8/10/12 bit binary word. The Output Enable control switches the outputs to a high impedance or off state when held high. The off state allows bus organized output connections.

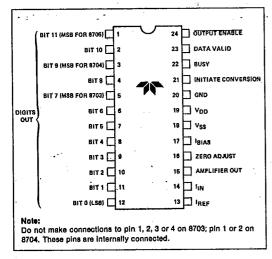

### **Pin Configuration**

### Ordering Information

| Part No.                            | Reso-<br>lution | Conv.<br>Tíme | Package               | Temp.<br>Range     |  |

|-------------------------------------|-----------------|---------------|-----------------------|--------------------|--|

| TSC8703CJ                           | 8-Bit           | 1.25 mSec     | 24-Pin<br>Plastic Dip | 0°C to<br>+70°C    |  |

| TSC8703CL                           | 8-Bit           | 1,25 mSec     | 24-Pin<br>CerDIP      | -40°C to<br>+85°C  |  |

| TSC8703BL                           | 8-Bit           | 1.25 mSec     | 24-Pin<br>CerDIP      | -55°C to<br>+125°C |  |

| TSC8704CJ                           | 10-Bit          | 5.0 mSec      | 24-Pin<br>Plastic Dip | 0°C to<br>+70°C    |  |

| TSC8704CL                           | 10-Bit          | 5.0 mSec      | 24-Pin<br>CerDIP      | -40°C to<br>+85°C  |  |

| TSC8704BL                           | 10-Bit          | 5.0 mSec      | 24-Pjn<br>CerDIP      | -55°C to<br>+125°C |  |

| TSC8705CJ                           | 12-Bit          | 20 mSec       | 24-Pin<br>Plastic Dip | 0°C to<br>+70°C    |  |

| TSC8705CN                           | 12-Bit          | 20 mSec       | 24-Pin<br>Ceramic     | -40°C to<br>+85°C  |  |

| TSC8705BN                           | 12-Bit          | 20 mSec       | 24-Pin<br>Ceramic     | -55°C to<br>+125°C |  |

| Devices with MIL-STD-883 Processing |                 |               |                       |                    |  |

| TSC8703BL/883                       | 8-Bit           | 1.25 mSec     | 24-Pin<br>CerDIP      | -55°C to<br>+125°C |  |

| TSC8704BL/883                       | 10-Bit          | 5.0 mSec      | 24-Pin<br>CerDIP      | -55°C to<br>+125°C |  |

| TSC8705BN/883                       | 12-Bit          | 20 mSec       | 24-Pin<br>Ceramic     | -55°C to           |  |

### **Handling Precautions**

The 8700 series are CMOS devices must be handled correctly to prevent damage. Package and store only in conductive foam, anti-static tubes or other conductive material. Use proper anti-static handling procedures. Do not connect in circuits under "power on" conditions, as high transients may cause permanent damage.

T-51-10-01

TSC8703 TSC8704 TSC8705

**Absolute Maximum Ratings**

| Storage Temperature Operating Temperature |                |

|-------------------------------------------|----------------|

| (BL, BN)                                  | 55°C to +125°C |

| (CL) Package                              | 40°C to + 85°C |

| (CJ) Package                              |                |

| Vpp -Vss                                  |                |

| lin                           |  |

|-------------------------------|--|

| Digital Input Voltage0.3 to \ |  |

| Operating Vpp and Vss Range   |  |

| Package Dissipation           |  |

| Lead Temperature              |  |

| (Soldering, 10 seconds)       |  |

Electrical Characteristics: Unless otherwise specified, V<sub>DD</sub> = +5 V, V<sub>SS</sub> = -5 V, V<sub>GND</sub> = 0, V<sub>REF</sub> = -6.4 V, R<sub>BIAS</sub> = 100 kΩ, test circuit shown. T<sub>A</sub> = 25°C unless Full Temperature Range is specified (-55°C to +125°C for BN and BL package, -40°C to +85°C for CL package, 0° to 70°C for CJ package).

| Bits<br>Bits<br>LSB        |

|----------------------------|

| Bits<br>Bits<br>LSB<br>LSB |

| LSB                        |

| Bits<br>Bits<br>LSB        |

| Bits<br>LSB<br>LSB         |

| LSB<br>LSB                 |

| LSB                        |

| LSB                        |

| LSB                        |

|                            |

| LSB                        |

| LSB                        |

|                            |

|                            |

|                            |

| ppm/° C                    |

|                            |

| % of                       |

| Nominal                    |

|                            |

| ppm/°C                     |

| pping C                    |

|                            |

|                            |

| mV                         |

| 1114                       |

|                            |

|                            |

|                            |

| mV                         |

|                            |

| <del></del>                |

|                            |

| mV                         |

|                            |

|                            |

| /9.0                       |

| ppm/°C                     |

| 5 0 0 0                    |

# TSC8703 TSC8704 TSC8705

# **BINARY OUTPUT ADCs**

T-51-10-01

**Electrical Characteristics (Cont.)**

| PARAMETER                                              | CONDITIONS                                                                | DEFINITION                                                                               | MIN              | ТҮР              | CJ/CN<br>MAX   | BN/B<br>MAX    | UNITS                    |

|--------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|------------------|----------------|----------------|--------------------------|

| Analog Inputs<br>I <sub>IN</sub> Full-Scale            |                                                                           | Full-Scale Analog Input Current<br>To Achieve Specified Accuracy                         | _                | 10               | -              | . –            | - μA                     |

| IREF<br>(Note 1)                                       |                                                                           | Reference Current Input To<br>Achieve Specified Accuracy                                 | _                | -20              |                | _              | μΑ                       |

| Digital Inputs VIN <sup>(1)</sup>                      | Fuli Temperature<br>Range                                                 | Logical "1" Input Threshold<br>For Initiate Conversion Input                             | 3.5              |                  | _              |                | V                        |

| VIN <sup>40)</sup>                                     | Full Temperature<br>Range                                                 | Logical "0" Input Threshold<br>For Initiate Conversion Input                             | _                |                  | 1.5            | 1.5            | ٧                        |

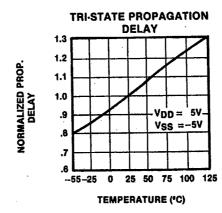

| Propagation Delay<br>Output Enable                     | C <sub>L</sub> = 100 pF, R <sub>L</sub> = 1 KΩ                            | Трін, Трні                                                                               |                  | 500              |                | 1,000          | . ns                     |

| Digital Outputs                                        | OE = 3.5 V.                                                               |                                                                                          |                  |                  |                |                |                          |

| lo(OFF)                                                | 0.4 V < Vc <2.4                                                           | Off-state Output Current                                                                 | -                | 0.1              | ±10            | ±10            | μΑ                       |

| Vout <sup>(1)</sup>                                    | Full Temp. Range<br>fout = -10 μA<br>fout = -500 μA                       | Logical "1" Output Voltage<br>For Digits Out, Busy, and<br>Data Valid Outputs            | 4.5<br>2.4       | =                | _              |                | v                        |

| Vour <sup>(0)</sup>                                    | Full Temp. Range<br>V <sub>DD</sub> = 4.75 V<br>I <sub>OUT</sub> = 500 µA | Logical "0" Output Voltage<br>For Digits Out, Busy, and<br>Data Valid Outputs            | -                | _                | 0.4            | 0.4            | V                        |

| Dynamic<br>Conversion Time                             | Full Temp. Range                                                          | Time Required to Perform One<br>Complete A/D Conversion<br>TSC8703<br>TSC8704<br>TSC8705 | =                | 1.25<br>5<br>20  | 1.8<br>6<br>24 | 1.8<br>6<br>24 | ms<br>ms<br>ms           |

| Conversion<br>Rate in<br>Free-Run Mode                 | VINT CONV = + 5 V                                                         | TSC8703<br>TSC8704<br>TSC8705                                                            | 555<br>167<br>42 | 800<br>200<br>50 | =              |                | Conv'ns<br>per<br>Second |

| Minimum Pulse Width for Initiate Conversion            | Full Temp. Range                                                          |                                                                                          | 500              | -                | _              | _              | ns                       |

| Supply Current IDD Quiescent (L/N Package) (J Package) | Full Temp. Range<br>Vเทт conv = 0V                                        | Current Required From Positive<br>Supply During Operation                                | =                | 1.4<br>1.4       | 2.5<br>5.0     | 3,5            | mA<br>mA                 |

| Iss Quiescent<br>(L/N Package)<br>(J Package)          | Full Temp. Range<br>VINIT CONV = 0V                                       | Current Required From Negative<br>Supply During Operation                                | =                | -1.6<br>-1.6     | -2.5<br>-5.0   | -3.5           | mA<br>mA                 |

| Supply Sensitivity                                     | V <sub>DD</sub> ± 1 V, V <sub>SS</sub> ±1 V                               | Change in Full-Scale Gain vs<br>Supply Voltage Change                                    |                  | ±0.5             | ±1.0           | ±1.0           | %/V                      |

|                                                        | V <sub>DD</sub>   =  V <sub>SS</sub>   = 5 V ± 1 V                        | Change in Full-Scale Gain vs Supply<br>Voltage Change for Tracking Supplies              |                  | ±0.05            | ±0.1           | ±0.1           | . %/\                    |

NOTE:

IN and IREF pins connect to the summing junction of an operational amplifier. Voltage sources cannot be attached directly but must be buffered by external resistors. See Test Circuit.

T-51-10-01

TSC8703 TSC8704 TSC8705

### **Circuit Description**

During conversion the sum of a continuous current I<sub>IN</sub> and pulses of a reference current I<sub>REF</sub> is integrated for a fixed number of clock periods. I<sub>IN</sub> is proportional to the analog input voltage; I<sub>REF</sub> is switched in for exactly one clock period just frequently enough to maintain the output of the integrator near zero. Thus, the charge from the continuous I<sub>IN</sub> current is balanced against the pulses of I<sub>REF</sub> current. The total number of I<sub>REF</sub> pulses needed during the conversion period to maintain the charge balance is counted, and the result (in Binary) is latched into the outputs at the end of the conversion.

The converter contains two counters and a clock in addition to an operational amplifier, comparator, latching output buffers and housekeeping logic. One counter is a clock counter which (after a reset pulse) starts counting clock pulses; when the required count is reached, the clock counter generates a pulse to start the end-of-conversion routine. The other counter is a data counter, which is reset synchronously with the clock counter and counts the number of times

the IREF current is switched into the summing Input of the amplifier during the period defined by the clock counter,

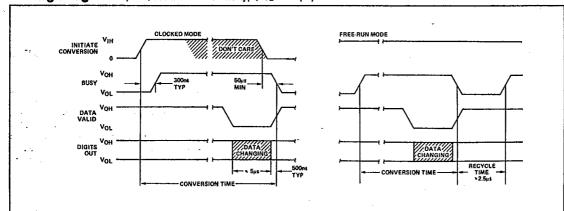

When the Initiate Conversion input is strobed with a positive signal, the busy line latches high and a 10  $\mu s$  (times given are approximate) start up cycle begins. The integrating capacitor is discharged and both counters are reset during this start up period. Conversion begins at the end of the reset pulse and ends with a pulse generated either by the clock counter or by an overflow condition in the data counter. This pulse disables further inputs into both counters and triggers a 10  $\mu$ s shutdown cycle. During the shutdown cycle Data Valid goes low for 5  $\mu$ s. This binary sequence is shown in the timing diagrams. Busy is true high, and when the circuit is busy, Initiate Conversion has no effect and may be high or low. Data Valid is also true high. The data from a conversion remain valid for as long as power is applied to the circuit or until Data Valid falls at the end of a subsequent conversion, at which time the output data are updated to reflect the latest conversion.

8

### Timing Diagrams (Rise, fall times = 200 ns typ., C<sub>L</sub> = 50 pF)

# TSC8704 TSC8705

### **BINARY OUTPUT ADCs**

T-51-10-01

# Pin Functions Initiate Conversion Input

Accepts CMOS and most 5 V logic inputs. Applying a logic "1" to the initiate Conversion pin initiates the A/D conversion cycle. Once conversion has been initiated, the cycle cannot be interrupted, and the initiate Conversion pin is disabled until conversion is complete. Two modes of operation are permitted, clocked or free-running. For clocked operation the initiate Conversion input is held at logic "0" for standby and taken to logic "1" when a conversion is desired. For free-running operation the initiate Conversion pin is connected to Vpp or similar permanent logic "1" voltage.

### **Busy Output**

A digital status output which is compatible with CMOS logic and low power TTL (can sink and source 500  $\mu\text{A}$ ). A logic "1" output on the Busy pin Indicates a conversion cycle is in process. A logic "1" to logic "0" transition indicates that conversion is complete and the result has been latched at the Digits Out pins. A logic "0" to logic "1" transition indicates a new conversion cycle has been initiated. If the device is operating in the free-running mode, the Busy output willi remain low for approximately 2.5  $\mu\text{s}$ , marking the completion and initiation of consecutive conversion cycles.

### **Data Valid Output**

A digital status which is compatible with CMOS logic and low power TTL (can sink and source 50  $\mu\text{A}$ ). A logic "1" output at the Data Valld pin indicates that the Digits Out pins are latched with the result of the last conversion cycle. The Data Valld output goes to logic "0" approximately 5  $\mu\text{s}$  before the completion of a conversion cycle. During this 5  $\mu\text{s}$  interval new data is being transferred to the Digits Out pins, and the Digits Out are not valid.

#### Digits Out (Bit 0, Bit 1, etc.)

The binary digit outputs which are the result of the A/D conversion. These outputs are CMOS logic and low power TTL compatible.

# Applications Information Input/Output Relationships

The analog input voltage ( $V_{\mbox{\scriptsize IN}}$ ) is related to the output by the transfer equation:

Digital Counts =

$$\frac{V_{IN} \cdot A \cdot R_{REF}}{R_{IN} \cdot V_{REF}}$$

A = 528 for 8703 A = 2064 for 8704 A = 8208 for 8705

where Digital Counts is the value of the binary output word presented at Digits Out pins in response to Vin.

The digital output code format is as follows:

| Analog<br>Input                | Digital<br>Output |

|--------------------------------|-------------------|

| •                              | MSB LSB           |

| V <sub>IN</sub> ≤ Full-Scale   | 1 111 1           |

| = Full-Scale -1 LSB<br>= 1 LSB | 11111             |

| ≤0                             | 00000             |

Two's complement coding can be generated by inverting the Most Significant Bit (MSB) signal.

### **External Component Selection**

Obtaining a high accuracy conversion system depends on the voltage regulation of VREF and the thermal stability of RIN and RREF. The exact dependence is given by the transfer function. System accuracy also depends, to a lesser degree, on the voltage regulation of VDD and Vss. The supply connections VDD and Vss should have bypass capacitors of value 0.1 µF or larger right at the device pins.

### RIN, REF

Values of these components are chosen to give a full-scale input current of approximately 10  $\mu$ A and a reference current of approximately –20  $\mu$ A.

Examples:

$$R_{IN} \approx \frac{10 \text{ V}}{10 \mu A} = 1 \text{ M } \Omega \qquad R_{REF} \approx \frac{-6.4 \text{ V}}{-20 \mu A} = 320 \text{ k} \Omega$$

Note that these values are approximations, and the exact relationships are defined by the transfer equation. In practice, the value of R<sub>IN</sub> typically would be trimmed using the optional gain adjust circuit to obtain full-scale output at V<sub>IN</sub> full-scale (see adjustment procedure). Metal film resistors with 1% tolerance or better are recommended for high accuracy applications because of their thermal stability and low noise generation.

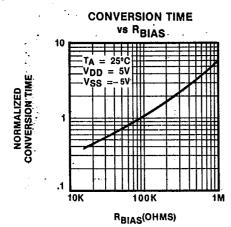

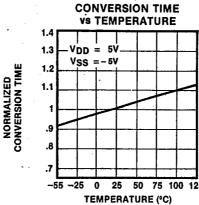

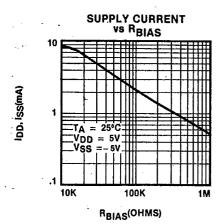

#### RBIAS

Specifications for the 87XX are based on RBIAS = 100 k $\Omega$  ±10% unless otherwise noted. However, there are instances when the designer may want to change this resistor in order to affect the conversion time and the supply current. By decreasing RBIAS the A/D will convert much faster and the supply current will be higher. (For example: When RBIAS is 20 k the conversion time is reduced by 1/3, and the supply current will increase from 2 mA to 7 mA.) Likewise, if the RBIAS is increased the conversion time will be longer and the supply current will be much lower. (For example: When RBIAS = 1 m $\Omega$  the conversion time will be six times longer, and supply current is now reduced to .5 mA). For details of this relationship refer to AN9 typical performance curves.

T-51-10-01

TSC8703 TSC8704 TSC8705

## **Applications Information (Cont.)**

### RDAMP

Exact value not critical but should have a nominal value of 100  $\Omega$  ±10%. Locate close to pin 14.

### CDAMP

Exact value not critical but should have a nominal value of 270 pF  $\pm$ 20%. Locate close to pin 14.

#### CINT

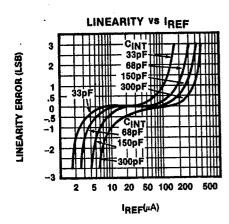

Exact value not critical but should have a nominal value of 68 pF  $\pm$  10%. Low leakage types are recommended, although mica or ceramic devices can be used in applications where their temperature limits are not exceeded. Locate as close as possible to pins 14, 15. For the TSC8703  $C_{INT}=33$  pF is adequate with Rapj = 1 k $\Omega$ .

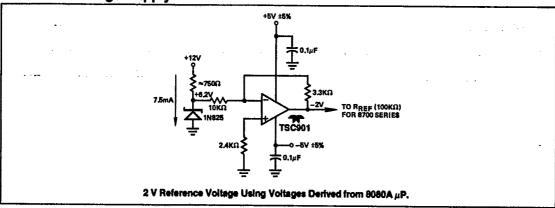

### VREF

A negative reference voltage must be supplied. This may be obtained from a constant current source circuit or from the negative supply.

### VDD, VSS

Power supplies of  $\pm 5$  V are recommended, with 0.05% line and load regulation and 0.1  $\mu$ F decoupling capacitors,

### **Adjustment Procedure**

The test circuit diagram shows optional circuits for trimming the zero location and full-scale gain. Because the digital outputs remain constant outside of the normal operating range (i.e. below zero and above full-scale), it is recommended that transition points be used in setting the zero and full-scale values. Recommended procedure is as follows:

- Set the initiate conversion control high to provide free-run operation and verify that converter is operating.

- Set V<sub>IN</sub> to +1/2 LSB and trim the zero adjust circuit to obtain a 000 . . . 000 . . . to 000 . . . 001 transition. This will correctly locate the zero end.

- For full-scale adjustment, set V<sub>IN</sub> to the full-scale value less 1 1/2 LSB and trim the gain adjust circuit for a 111 . . . 110 to 111 . . . 111 transition.

If adjustments are performed in this order, there should be no interaction and they should not have to be repeated.

8

# TSC8703 TSC8704 TSC8705

# **BINARY OUTPUT ADCs**

T-51-10-01

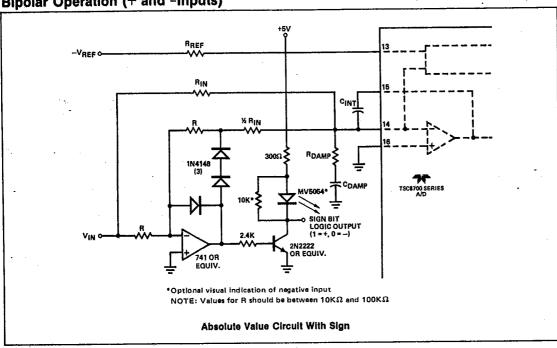

Application/Design Circuits Bipolar Operation (+ and -Inputs)

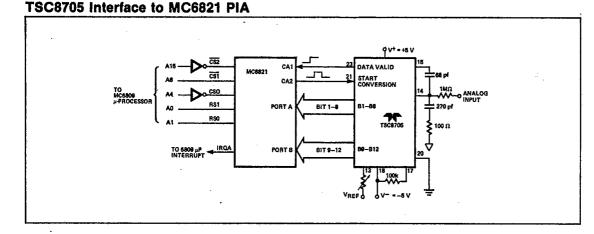

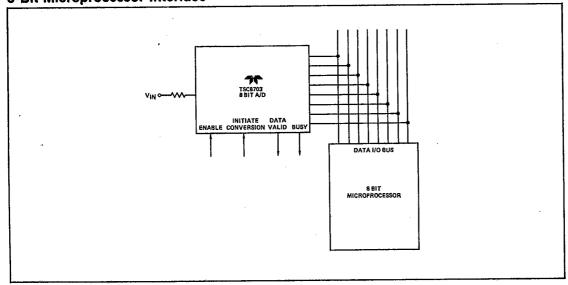

8-Bit Microprocessor Interface

T-51-10-01

**TSC8703 TSC8704 TSC8705**

8

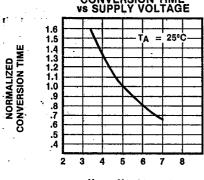

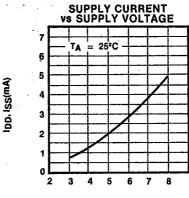

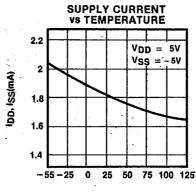

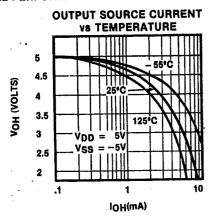

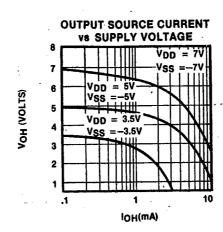

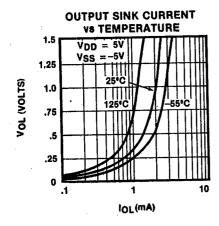

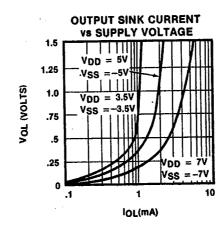

### **TYPICAL PERFORMANCE CURVES**

CONVERSION TIME VS SUPPLY VOLTAGE

VDD = VSS(VOLTS)

VDD = VSS(VOLTS)

TEMPERATURE(°C)

8-139

TSC8703 TSC8704 TSC8705

## **BINARY OUTPUT ADCs**

T-51-10-01

TYPICAL PERFORMANCE CURVES

8-140

8

**Application/Design Circuits (Cont.)**

**Reference Voltage Supply**

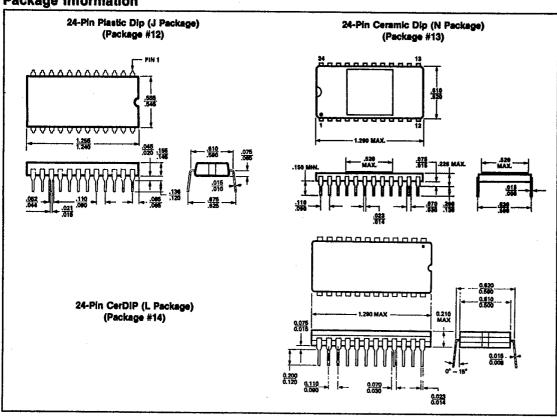

**Package Information**

8-141