# 4096 x 1-BIT DYNAMIC RAM

Processed to MIL-STD-883, Method 5004, Class B

# MKB4027(J)-83/84

#### **FEATURES**

- □ Extended operating temperature range (-55°C ≤ T<sub>A</sub> ≤ +85°C)

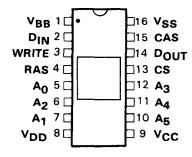

- ☐ Industry standard 16-pin DIP (MK4096) configuration

- □ 200ns access time, 375ns cycle (-83) 250ns access time, 375ns cycle (-84)

- $\Box \pm 10\%$  tolerance on all supplies (+12V,  $\pm 5$ V)

- □ Low Power: 467mW active (max) 40mW standby (max)

#### DESCRIPTION

The MKB4027 is a 4096 word by 1 bit MOS random access memory circuit fabricated with Mostek's N-channel silicon gate process. This process allows the MKB4027 to be a high performance state-of-the-art memory circuit that is manufacturable in high volume. The MKB4027 employs a single transistor storage cell utilizing a dynamic storage technique and dynamic control circuitry to achieve optimum performance with low power dissipation.

A unique multiplexing and latching technique for the address inputs permits the MKB4027 to be packaged in a standard 16-pin DIP on 0.3 in. centers. This package size provides high system-bit densities and is compatible

- ☐ Improved performance with "gated CAS," "RAS only" refresh and page mode capability

- ☐ All inputs are low capacitance and TTL compatible

- Input latches for addresses, chip select and data in

- ☐ Three-state TTL compatible output

- ☐ Output data latched and valid into next cycle

- ☐ Ruggedized for use in severe military environments

with widely available automated testing and insertion equipment.

System oriented features include direct interfacing capability with TTL, only 6 very low capacitance address lines to drive, on-chip address and data registers which eliminates the need for interface registers, input logic levels selected to optimize noise immunity, and two chip select methods to allow the user to determine the appropriate speed/power characteristics of his memory system. The MKB4027 also incorporates several flexible operating modes. In addition to the usual read and write cycles, read-modify write, page-mode, and RAS only refresh cycles are available with the MKB4027. Page-mode timing is very useful in systems requiring Direct Memory Access (DMA) operation.

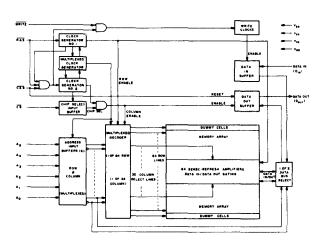

## **FUNCTIONAL DIAGRAM**

# PIN CONNECTIONS

#### PIN NAMES

| A <sub>0</sub> - A <sub>6</sub> | Address Inputs     | WRITE           | Read/Write Input |

|---------------------------------|--------------------|-----------------|------------------|

| CS                              | Col Address Strobe | ∨ <sub>BB</sub> | Power (-5V)      |

| D <sub>IN</sub>                 | Data In            | Vcc             | Power (+5V)      |

| DOUT                            | Data Out           | $V_{DD}$        | Power (+12V)     |

| RAS                             | Row Address Strobe | ∨ <sub>SS</sub> | Ground           |

|                                 |                    |                 |                  |

# **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>BB</sub>                            | 0.5V to +20V   |

|---------------------------------------------------------------------------|----------------|

| Voltage on VDD, VCC relative to VSS                                       |                |

| V <sub>BB</sub> - V <sub>SS</sub> (V <sub>DD</sub> - V <sub>SS</sub> > 0) |                |

| Operating Temperature (Ambient)(Ceramic)                                  | 55°C to +85°C  |

| Storage Temperature (Ambient)(Ceramic)                                    | 65°C to +150°C |

| Short Circuit Output Current                                              | 50mA           |

| Power Dissination                                                         |                |

<sup>\*</sup>Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **RECOMMENDED DC OPERATING CONDITIONS<sup>4</sup>**

$(-55^{\circ}C \le T_{A} \le 85^{\circ}C)$

| SYM             | PARAMETER                                          | MIN  | TYP  | MAX  | UNITS | NOTES |

|-----------------|----------------------------------------------------|------|------|------|-------|-------|

| $V_{DD}$        | Supply Voltage                                     | 10.8 | 12.0 | 13.2 | V     | 2     |

| V <sub>CC</sub> | Ground                                             | 4.5  | 5.0  | 5.5  | V     | 2,3   |

| V <sub>SS</sub> | Supply Voltage                                     | 0    | 0    | 0    | V     | 2     |

| V <sub>BB</sub> | Supply Voltage                                     | -4.5 | -5.0 | -5.5 | V     | 2     |

| VIHC            | Logic 1 Voltage, RAS, CAS, WRITE                   | 2.7  |      | 7.0  | V     | 2     |

| VIH             | Logic 1 Voltage, all inputs except RAS, CAS, WRITE | 2.4  |      | 7.0  | V     | 2     |

| V <sub>IL</sub> | Logic O Voltage, all inputs                        | -1.0 |      | .8   | V     | 2     |

### DC ELECTRICAL CHARACTERISTICS4

$(-55^{\circ}\text{C} \le \text{T}_{A} \le 85^{\circ}\text{C})^{1} \text{ (V}_{DD} = 12.0\text{V} \pm 10\%; \text{ V}_{CC} = 5.0\text{V} \pm 10\%; \text{ V}_{SS} = 0\text{V}; \text{ V}_{BB} = -5.0\text{V} \pm 10\%)$

| SYM               | PARAMETER                                                          | MIN | TYP | MAX | UNITS | NOTES |

|-------------------|--------------------------------------------------------------------|-----|-----|-----|-------|-------|

| I <sub>DD1</sub>  | Avg. V <sub>DD</sub> Power Supply Current                          |     |     | 35  | mA    | 5     |

| I <sub>DD2</sub>  | Standby V <sub>DD</sub> Power Supply<br>Current                    |     |     | 3.0 | mA    | 8     |

| lDD3              | Avg. V <sub>DD</sub> Power Supply Current during "RAS only" cycles |     |     | 27  | mA    |       |

| lcc               | V <sub>CC</sub> Power Supply Current                               |     |     |     | mA    | 6     |

| I <sub>BB</sub>   | Avg. V <sub>BB</sub> Power Supply Current                          |     |     | 200 | μΑ    |       |

| I <sub>(L)</sub>  | Input Leakage Current (any input)                                  |     |     | 10  | μΑ    | 7     |

| I <sub>O(L)</sub> | Output Leakage Current                                             |     |     | 10  | μΑ    | 8,9   |

| Vон               | Output Logic 1 Voltage @ I <sub>OUT</sub> = -5mA                   | 2.4 |     |     | ٧     |       |

| V <sub>OL</sub>   | Output Logic 0 Voltage @ I <sub>OUT</sub> = 3.2mA                  |     |     | 0.4 | V     |       |

#### NOTES:

- T<sub>A</sub> is specified for operation at frequencies to t<sub>R</sub>C≥t<sub>R</sub>C (min). Operation at higher cycle rates with reduced ambient temperatures and higher power dissipation is permissible provided that all AC parameters are met.

- 2. All voltages referenced to VSS.

- Output voltage will swing from V<sub>SS</sub> to V<sub>CC</sub> when enabled, with no output load. For purposes of maintaining data in standby mode, V<sub>CC</sub> may be reduced to V<sub>SS</sub> without affecting refresh operations or data retention. However, the V<sub>OH</sub> (min) specification is not guaranteed in this mode.

- Several cycles are required after power-up before proper device operation is achieved. Any 8 cycles which perform refresh are adequate for this purpose.

- Current is proportional to cycle rate. I<sub>DD1</sub> (max) is measured at the cycle rate specified by t<sub>RC</sub> (min). See Figure 1 for I<sub>DD1</sub> limits at other cycle rates.

- I<sub>CC</sub> depends on output loading. During readout of high level data V<sub>CC</sub> is connected through a low impedance (135Ω typ) to Data Out. At all other times I<sub>CC</sub> consists of leakage currents only.

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (4,11,7)

(-55°C  $\leq$  T  $_{A}$   $\leq$  85°C)1 (V  $_{DD}$  = 12.0V  $\pm$  10%, V  $_{CC}$  = 0V, V  $_{BB}$  = -5.0V  $\pm$  10%)

|                    |                                            | MKB4027-83 MKB402 |      | 27-84 |      |       |       |

|--------------------|--------------------------------------------|-------------------|------|-------|------|-------|-------|

| SYM                | PARAMETER                                  | MIN               | MAX  | MIN   | MAX  | UNITS | NOTES |

| tRC                | Random read or write cycle time            | 375               |      | 380   |      | ns    | 12    |

| <sup>t</sup> RWC   | Read-write cycle time                      | 375               |      | 395   |      | ns    | 12    |

| tRMW               | Read Modify Write Cycle                    | 405               |      | 470   |      | ns    | 12    |

| <sup>t</sup> PC    | Page mode cycle time                       | 225               |      | 285   |      | ns    | 12    |

| tRAC               | Access time from row address strobe        |                   | 200  |       | 250  | ns    | 13,15 |

| <sup>t</sup> CAC   | Access time from column address strobe     |                   | 135  |       | 165  | ns    | 14,15 |

| <sup>t</sup> OFF   | Output buffer turn-off delay               |                   | 50   |       | 60   | ns    |       |

| tRP                | Row address strobe precharge time          | 120               |      | 120   |      | ns    |       |

| t <sub>FI</sub> AS | Row address and strobe pulse width         | 200               | 5000 | 250   | 5000 | ns    |       |

| tRSH               | Row address strobe hold time               | 135               |      | 165   |      | ns    |       |

| t <sub>CAS</sub>   | Column address strobe pulse width          | 135               |      | 165   |      | ns    |       |

| <sup>t</sup> CSH   | CAS hold time                              | 200               |      | 250   |      | ns    |       |

| <sup>t</sup> RCD   | Row to column strobe delay                 | 25                | 65   | 35    | 85   | ns    | 16    |

| <sup>t</sup> ASR   | Row address set-up time                    | 0                 |      | 0     |      | ns    |       |

| <sup>t</sup> RAH   | Row address hold time                      | 25                |      | 35    |      | ns    |       |

| <sup>t</sup> ASC   | Column address set-up time                 | 0                 |      | 0     |      | ns    |       |

| <sup>t</sup> CAH   | Column address hold-time                   | 55                |      | 75    |      | ns    |       |

| <sup>t</sup> AR    | Column address hold time referenced to RAS | 120               |      | 160   |      | ns    |       |

| tcsc               | Chip select set-up time                    | 0                 |      | 0     |      | ns    |       |

| <sup>t</sup> CH    | Chip select hold time                      | 55                |      | 75    |      | ns    |       |

| <sup>t</sup> CHR   | Chip select hold time referenced to RAS    | 120               |      | 160   |      | ns    |       |

| tŢ                 | Transition time (rise and fall)            | 3                 | 50   | 3     | 50   | ns    | 17    |

| <sup>t</sup> RCS   | Read command set-up time                   | 0                 |      | 0     |      | ns    |       |

| <sup>t</sup> RCH   | Read command hold time                     | 0                 |      | 0     |      | ns    |       |

| tWCH               | Write command hold time                    | 55                |      | 75    |      | ns    |       |

| <sup>t</sup> WCR   | Write command hold time referenced to RAS  | 120               |      | 160   |      | ns    |       |

| <sup>t</sup> WP    | Write command pulse width                  | 55                |      | 75    |      | ns    |       |

| <sup>t</sup> RWL   | Write command to row strobe lead time      | 70                |      | 85    |      | ns    |       |

| <sup>t</sup> CWL   | Write command to column strobe lead time   | 70                |      | 85    |      | ns    |       |

| <sup>t</sup> DS    | Data in set-up time                        | 0                 |      | 0     |      | ns    | 18    |

# **ELECTRICAL CHARACTERISTICS (Continued)**

|                   | PARAMETER                           | MKB4 | MKB4027-83 |     | MKB4027-84 |       |       |

|-------------------|-------------------------------------|------|------------|-----|------------|-------|-------|

| SYM               |                                     | MIN  | MAX        | MIN | MAX        | UNITS | NOTES |

| <sup>t</sup> DH   | Data in hold time                   | 55   |            | 75  |            | ns    | 18    |

| <sup>t</sup> DHR  | Data in hold time referenced to RAS | 120  |            | 160 |            | ns    |       |

| tCRP              | Column to row strobe precharge time | 0    |            | 0   |            | ns    |       |

| tCP               | Column precharge time               | 80   |            | 110 |            | ns    |       |

| <sup>t</sup> RFSH | Refresh Period                      |      | 2          |     | 2          | ms    |       |

| twcs              | Write command set-up time           | 0    |            | 0   |            |       | 19    |

| tCWD              | CAS to WRITE delay                  | 80   |            | 80  |            | ns    | 19    |

| tRWD              | RAS to WRITE delay                  | 145  |            | 175 |            | ns    | 19    |

| tDOH              | Data out hold time                  | 5    |            | 5   |            | μS    |       |

## NOTES (Continued)

- All device pins at 0 volts except V<sub>BB</sub> which is at -5 volts and the pin under test which is at -10 volts.

- Output logic is disabled (high-impedance) and RAS and CAS are both at a logic 1. Transient stabilization is required prior to measurement of this parameter

- 9. 0V :- V<sub>OUT</sub> 1 -10V

- 10. Effective capacitance is calculated from the equation C  $\frac{\Delta Q}{V}$  with  $\Delta V = 3$  Volts

- 11 AC measurements assume t<sub>1</sub> 5ns

- 12 The specification for t<sub>RC</sub> (min) and t<sub>RWC</sub> (min) are used only to indicate cycle time at which proper operation over the full temperature range (+55 C \*\* T<sub>A</sub> \*\* 85 C) is assured. See Figure 2 for derating curve.

- 13 Assumes that tRCD : tRCD (max)

- 14 Assumes that tRCD 'tRCD (max)

- 15. Measured with a load circuit equivalent to 2 TTL loads and 100pF.

- 16 Operation within the t<sub>RAC</sub> (max) limit insures that t<sub>RCD</sub> (max) is specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 17 V<sub>IHC</sub> (min) or V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IHC</sub> or V<sub>IH</sub> and V<sub>II</sub>

- 18 These parameters are referenced to CAS leading edge in random write cycles to WRITE leading edge in delayed write or read-modify-write cycles.

- 19 t<sub>WCS</sub>. t<sub>CWD</sub>. and t<sub>RWD</sub> are restrictive operating parameters in a read: write or read/modify/write cycle only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min), the cycle is an early write cycle and the Data Out will contain the data written into the selected cell. If t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min), the cycle is a read-write cycle and Data Out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of Data Out (at access time) is indetermined.

## **AC ELECTRICAL CHARACTERISTICS**

$(-55^{\circ}C \le T_{A} \le 85^{\circ}C)^{1}$   $(V_{DD} = 12.0V \pm 10\%, V_{CC} = 5V \pm 10\%, V_{SS} = 0V, V_{BB} = -5.0V \pm 10\%)$

| SYM             | PARAMETER                                                                                      | TYP | MAX | UNITS | NOTES |

|-----------------|------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| C <sub>I1</sub> | Input Capacitance (A <sub>O</sub> - A <sub>5</sub> ), D <sub>IN</sub> , $\overline{\text{CS}}$ | 4   | 5   | pF    | 10    |

| C <sub>I2</sub> | Input Capacitance RAS, CAS, WRITE                                                              | 8   | 10  | pF    | 10    |

| СО              | Output Capacitance (D <sub>OUT</sub> )                                                         | 5   | 7   | pF    | 8,10  |

SUPPLEMENTAL DATA SHEET TO BE USED IN CONJUNCTION WITH MOSTEK MK4027(J)-1/2/3 and MK4027(J)-4 DATA SHEETS