|                         |                                                                                |           |         |                                      |                                   |        |         | F     | REVISI                                                             | ONS  |    |      |                 |      |                    |                    |                   |        |         |     |

|-------------------------|--------------------------------------------------------------------------------|-----------|---------|--------------------------------------|-----------------------------------|--------|---------|-------|--------------------------------------------------------------------|------|----|------|-----------------|------|--------------------|--------------------|-------------------|--------|---------|-----|

| LTR                     |                                                                                |           |         |                                      | I                                 | DESCR  | RIPTIO  | N     |                                                                    |      |    |      | DATE (YR-MO-DA) |      |                    | DA)                | APPROVED          |        |         |     |

| A                       | Char                                                                           | nges in   | accord  | lance w                              | vith NO                           | R 5962 | 2-R006- | -98   |                                                                    |      |    |      | 98-01-22        |      |                    | Monica L. Poelking |                   |        |         |     |

| В                       | Char                                                                           | iges in   | accord  | lance w                              | nce with NOR 5962-R111-98         |        |         |       |                                                                    |      |    | 98-0 | )5-22           |      | Monica L. Poelking |                    |                   |        |         |     |

| С                       | Add o                                                                          | device    | 02. Ed  | litorial o                           | orial changes throughout.         |        |         |       |                                                                    |      |    | 98-0 | 07-01           |      | Monica L. Poelking |                    |                   |        |         |     |

| D                       | Upda                                                                           | ate boile | erplate | e to MIL-PRF-38535 requirements CF   |                                   |        |         |       | - CFS                                                              |      |    |      |                 | 05-1 | 10-04              |                    | -                 | Thomas | s M. He | ess |

|                         |                                                                                |           |         |                                      |                                   |        |         |       |                                                                    |      |    |      |                 |      |                    |                    |                   |        |         |     |

| REV                     | D                                                                              | D         | D       | D                                    |                                   |        |         |       |                                                                    |      |    |      |                 |      |                    |                    |                   |        |         |     |

| SHEET                   | 35                                                                             | 36        | 37      | 38                                   |                                   |        |         |       |                                                                    |      |    |      |                 |      |                    |                    |                   |        |         |     |

| REV                     | D                                                                              | D         | D       | D                                    | D                                 | D      | D       | D     | D                                                                  | D    | D  | D    | D               | D    | D                  | D                  | D                 | D      | D       | D   |

| SHEET                   | 15                                                                             | 16        | 17      | 18                                   | 19                                | 20     | 21      | 22    | 23                                                                 | 24   | 25 | 26   | 27              | 28   | 29                 | 30                 | 31                | 32     | 33      | 34  |

| REV STATUS              |                                                                                |           |         | REV                                  |                                   |        | D       | D     | D                                                                  | D    | D  | D    | D               | D    | D                  | D                  | D                 | D      | D       | D   |

| OF SHEETS               |                                                                                |           |         | SHE                                  |                                   |        | 1       | 2     | 3                                                                  | 4    | 5  | 6    | 7               | 8    | 9                  | 10                 | 11                | 12     | 13      | 14  |

| PMIC N/A                |                                                                                |           |         | PRE                                  | PAREI<br>T                        |        | M. He   | SS    |                                                                    |      | D  | EFEN | ISE S           | UPPL | Y CE               | NTEF               |                   | .UMB   | US      |     |

| STAI<br>MICRO<br>DRA    |                                                                                | CUIT      |         | CHE                                  | CKED<br>T                         |        | M. He   | SS    |                                                                    |      |    | C    | OLUN<br>http    |      |                    | O 432<br>scc.dl    |                   | 990    |         |     |

|                         |                                                                                |           |         | APP                                  | ROVE                              | D BY   |         |       |                                                                    | 1    |    |      |                 |      |                    |                    |                   |        |         |     |

| FOR US<br>DEPAR         | THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS                     |           |         |                                      | APPROVED BY<br>Monica L. Poelking |        |         |       | MICROCIRCUIT, DIGITAL, CMOS, 32-BIT<br>INTEGRATED MICROCONTROLLER, |      |    |      |                 |      |                    |                    |                   |        |         |     |

|                         | AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE DRAWING APPROVAL DATE<br>94-10-17 |           |         |                                      |                                   | MO     | NOL     | ITHIC | C SIL                                                              | ICON | 1  |      |                 |      |                    |                    |                   |        |         |     |

| AMSC N/A REVISION LEVEL |                                                                                |           |         | SIZE CAGE CODE<br>A 67268 5962-91501 |                                   |        |         |       |                                                                    |      |    |      |                 |      |                    |                    |                   |        |         |     |

| AM                      |                                                                                | ì         |         | REV                                  | ISION                             |        |         |       |                                                                    |      |    |      |                 |      |                    | !                  | 5962 <sup>.</sup> | -9150  | )1      |     |

# 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

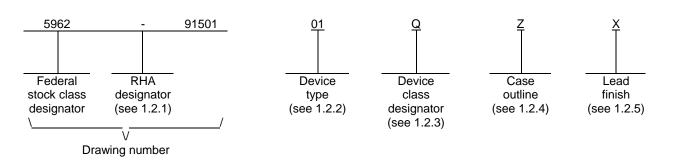

1.2 <u>PIN</u>. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | <u>Generic number</u> | Circuit function                  |

|-------------|-----------------------|-----------------------------------|

| 01          | 68332 <u>1</u> /      | 32-bit integrated microcontroller |

| 02          | 68332-20 <u>1</u> /   | 32-bit integrated microcontroller |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class       |                                | Device re           | quirements documentation                                                                                    |  |

|--------------------|--------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------|--|

| Μ                  |                                |                     | to the requirements for MIL-STD-883 compliant, non-<br>ircuits in accordance with MIL-PRF-38535, appendix A |  |

| Q or V             | Certifica                      | ation and qualifica | ation to MIL-PRF-38535                                                                                      |  |

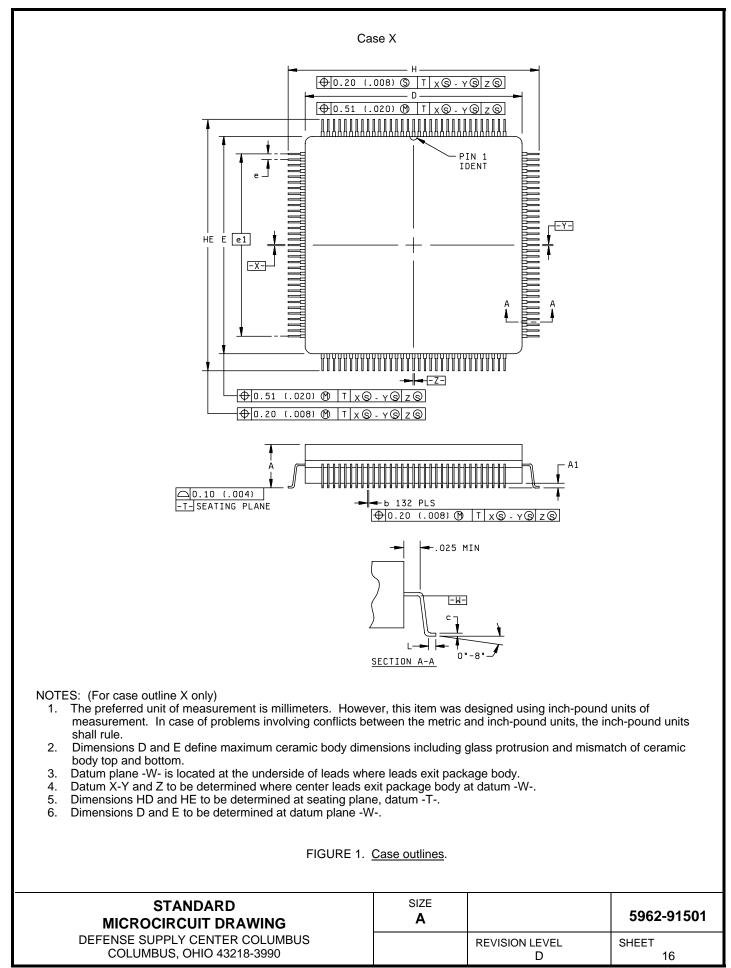

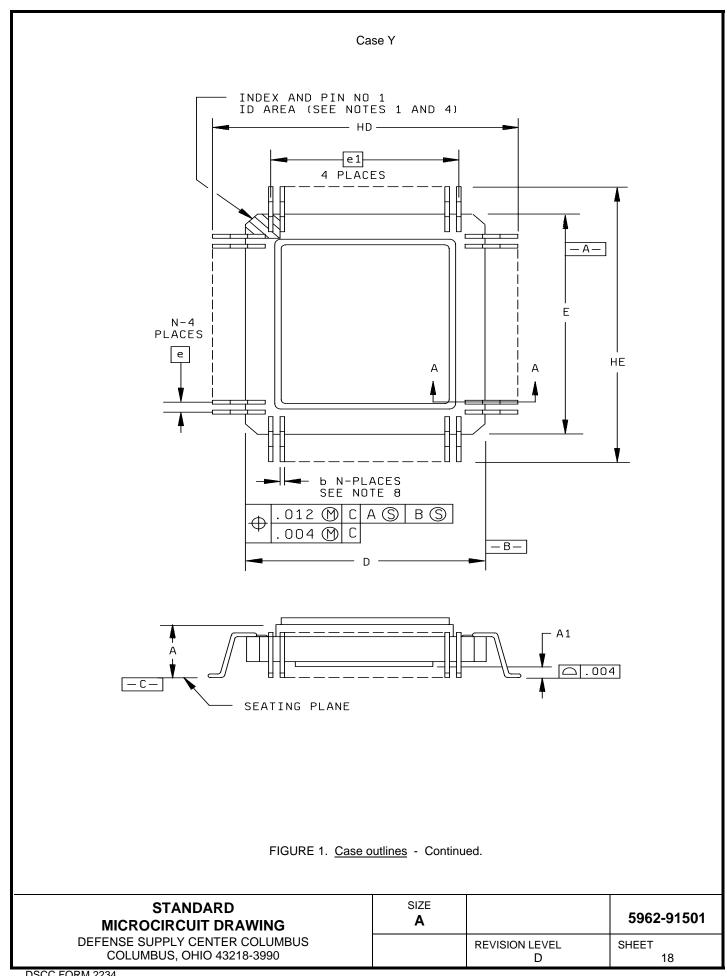

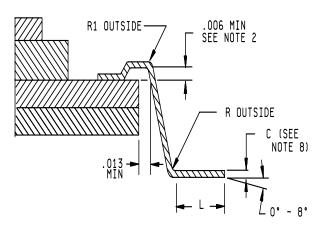

| 4 Case outline(s). | The case outline(s) are as dea | signated in MIL-S   | TD-1835 and as follows:                                                                                     |  |

| Outline letter     | Descriptive designator         | <u>Terminals</u>    | Package style                                                                                               |  |

| 7                  | CMC 45 D122                    | 100                 | Din grid orrow                                                                                              |  |

| Z | CMGA5-P132   | 132 | Pin grid array                |

|---|--------------|-----|-------------------------------|

| Х | See figure 1 | 132 | Gull wing leaded chip carrier |

| Y | See figure 1 | 132 | Gull wing leaded chip carrier |

|   |              |     |                               |

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

1/ This part does not include the Quadrature Decoder (QDEC) function.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-91501 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>D | SHEET 2    |

1.2.4

| 1.:                                       | 3 <u>Absolute maximum ratings</u> . <u>1</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|                                           | Storage temperature range (T <sub>STG</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        | 55°C to +150°C                                                                                                                                                            |                                                                                                             |

|                                           | Supply voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        | 0.3 V dc to +6.5                                                                                                                                                          | V dc <u>1/2/3</u> /                                                                                         |

|                                           | Input voltage range (V <sub>IN</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | Instantaneous maximum current single pin limit (applies t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | o all pins)                                                                                                                                            | 25 mA <u>1/ 2</u> / <u>3</u> /                                                                                                                                            | <u>5</u> /                                                                                                  |

|                                           | Power dissipation (P <sub>D</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        | 690 mW                                                                                                                                                                    |                                                                                                             |

|                                           | Operating maximum current digital input disruptive currer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nt range                                                                                                                                               |                                                                                                                                                                           |                                                                                                             |

|                                           | $V_{SS}$ – $0.3 \leq V_{IN} \leq V_{DD}$ + $0.3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        | 500 μA to +500 μ                                                                                                                                                          | uA <u>5/6/7</u> /                                                                                           |

|                                           | Thermal resistance, junction-to-case ( $\theta_{JC}$ ):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | Case Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        | 10°C/W                                                                                                                                                                    |                                                                                                             |

|                                           | Case X and Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                        | 10°C/W                                                                                                                                                                    |                                                                                                             |

|                                           | Lead temperature range (soldering, 5 seconds)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        | 270°C                                                                                                                                                                     |                                                                                                             |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

| 1.4                                       | 4 Recommended operating conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | Case operating temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        | 55°C to +125°C                                                                                                                                                            |                                                                                                             |

|                                           | Supply voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |                                                                                                                                                                           | 5.50 V dc                                                                                                   |

|                                           | PLL reference frequency range (f <sub>REF</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | System frequency: 8/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | Device 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | 16.78 MHz                                                                                                                                                                 |                                                                                                             |

|                                           | Device 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | On-chip PLL system frequency (f <sub>SYS</sub> ):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | Device 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | 0.131 ≤ f <sub>SYS</sub> ≤ 16                                                                                                                                             | 78 MHz                                                                                                      |

|                                           | Device 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | External clock operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | 0.0                                                                                                                                                                       |                                                                                                             |

|                                           | Device 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | 16.78 MHz                                                                                                                                                                 |                                                                                                             |

|                                           | Device 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | 20.97 MHz                                                                                                                                                                 |                                                                                                             |

|                                           | PLL lock time (t <sub>LPLL</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        | 20 ms <u> <u>9</u>/</u>                                                                                                                                                   |                                                                                                             |

|                                           | Limp mode clock frequency (f <sub>LIMP</sub> ): <u>10</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | SYNCR X bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           | SYNCR X bit = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        | f <sub>SYS</sub> max MHz                                                                                                                                                  |                                                                                                             |

|                                           | CLKOUT stability (C <sub>STAB</sub> ): <u>11/</u> <u>12</u> /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        | 1.00/ 1- 11.00/                                                                                                                                                           |                                                                                                             |

|                                           | Short term<br>Long term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |                                                                                                                                                                           |                                                                                                             |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        | -0.5% 10 +0.5%                                                                                                                                                            |                                                                                                             |

| 2/<br>3/<br>4/<br>5/<br>6/<br>7/<br>8/    | Permanent damage can occur if maximum ratings are excere<br>recommended values affects device reliability. Device mod<br>extremes.<br>Although sections of the device contain circuitry to protect a<br>normal precautions to avoid exposure to voltages higher tha<br>This parameter is periodically sampled rather than 100% ter<br>All pins except TSTME/TSC.<br>All functional non-supply pins are internally clamped to $V_{SS}$ .<br>internally clamped to $V_{DD}$ .<br>Power supply must maintain regulation within operating $V_{DD}$<br>conditions.<br>Total input current for all digital input-only and all digital input<br>cause disruption of normal operation.<br>All internal registers retain data at 0 Hz.                                   | ules may not oper<br>against damage fro<br>an maximum-rated<br>sted.<br>All functional pins<br>range during insta<br>ut/output pins mus                | ate normally while being exom high static voltages or end voltages.<br>I voltages.<br>s except EXTAL, TSTME/T<br>antaneous and operating m<br>t not exceed 10 mA. Excert  | posed to electrical<br>lectrical fields, take<br>SC, and XFC are<br>haximum current<br>eding this limit can |

| <u>10</u> /<br><u>11</u> /<br><u>12</u> / | Assumes that stable $V_{DDSYN}$ is applied, that an external filter<br>that the crystal oscillator is stable. Lock time is measured fit<br>the period required for PLL lock after changing the W and Y<br>(SYNCR) while the PLL is running, and to the period required<br>Determine by the internal reference voltage applied to the o<br>prescaler on the system clock output.<br>Short-term CLKOUT stability is the average deviation from p<br>maximum f <sub>SYS</sub> . Long-term CLKOUT stability is the average<br>interval at maximum f <sub>SYS</sub> . Stability is measured with a stabl<br>frequency is additive to this figure.<br>This parameter is periodically sampled rather than 100% ter<br>Values will be added when they become available. | rom power-up to re<br>' frequency control<br>ed for the clock to<br>in-chip VCO. The<br>programmed frequ<br>deviation from pro-<br>e external clock in | eset release. This specifica<br>I bits in the synthesizer con<br>lock after LPSTOP.<br>X-bit in SYNCR controls a<br>uency measured over a 2 Fa<br>ogrammed frequency meas | ation also applies to<br>trol register<br>divide by two<br>s interval at<br>ured over a 1 ms                |

|                                           | STANDARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SIZE                                                                                                                                                   |                                                                                                                                                                           |                                                                                                             |

|                                           | MICROCIRCUIT DRAWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Α                                                                                                                                                      |                                                                                                                                                                           | 5962-91501                                                                                                  |

|                                           | DEFENSE SUPPLY CENTER COLUMBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                           | QUEET                                                                                                       |

|                                           | COLUMBUS, OHIO 43218-3990                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        | REVISION LEVEL<br>D                                                                                                                                                       | SHEET<br>3                                                                                                  |

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits. MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

## DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein and on figure 1.

3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

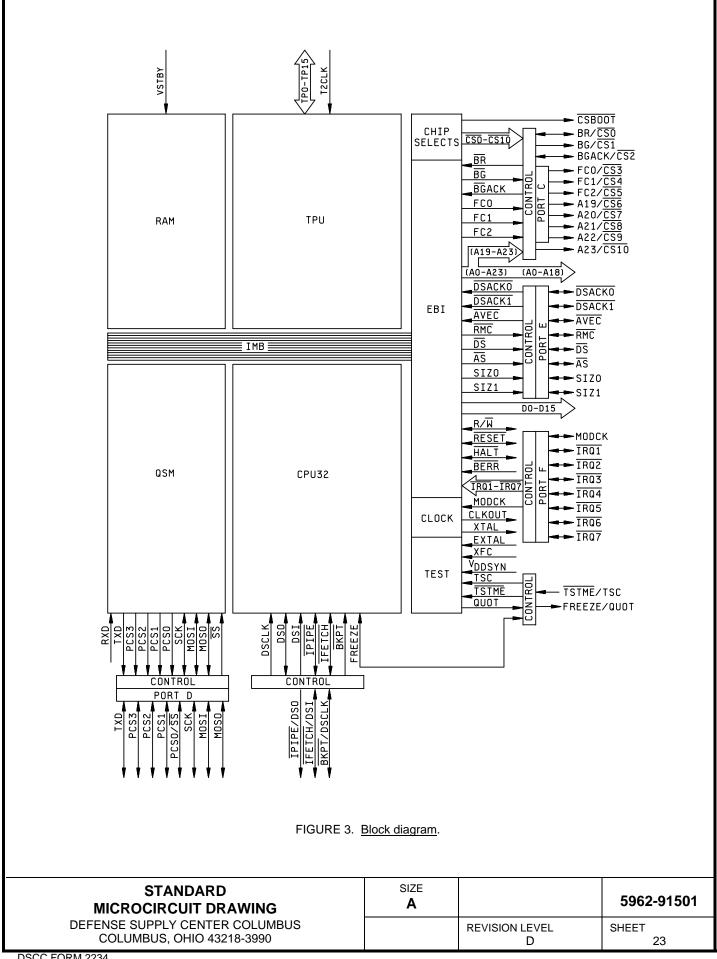

3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

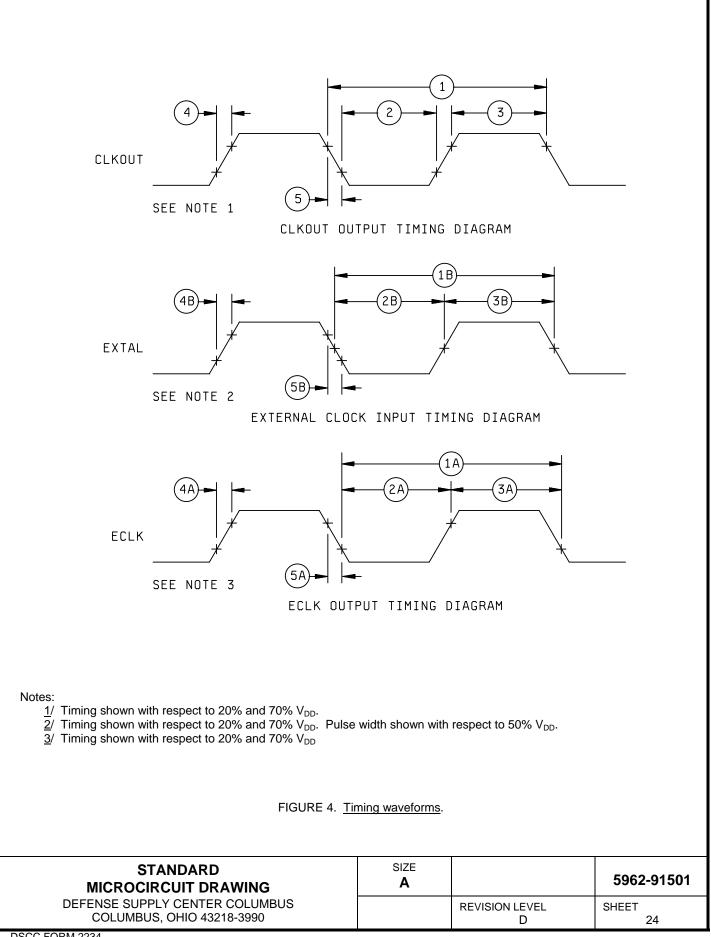

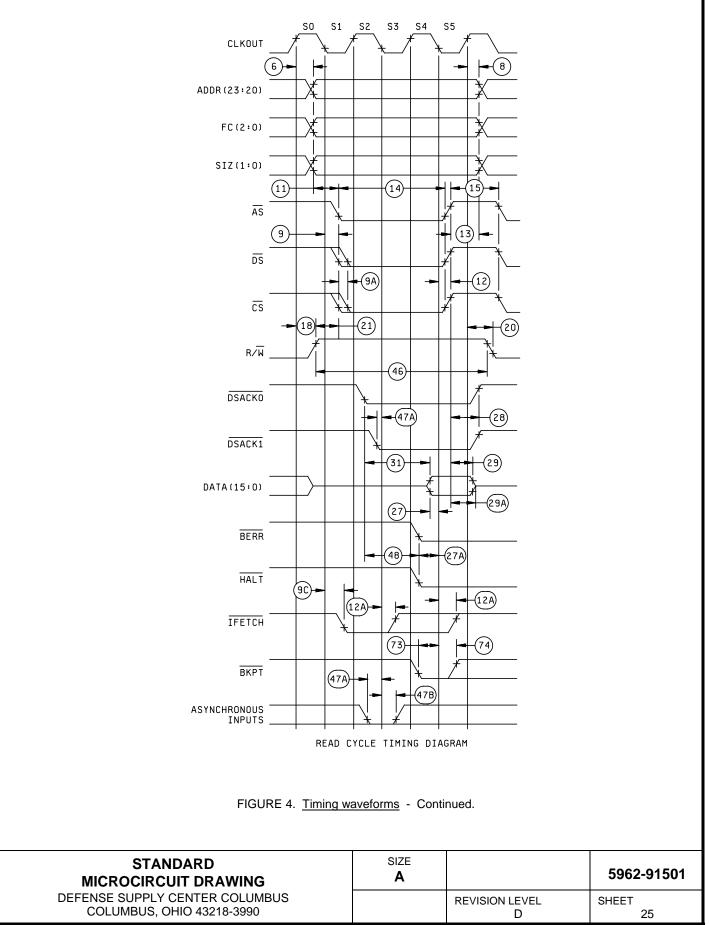

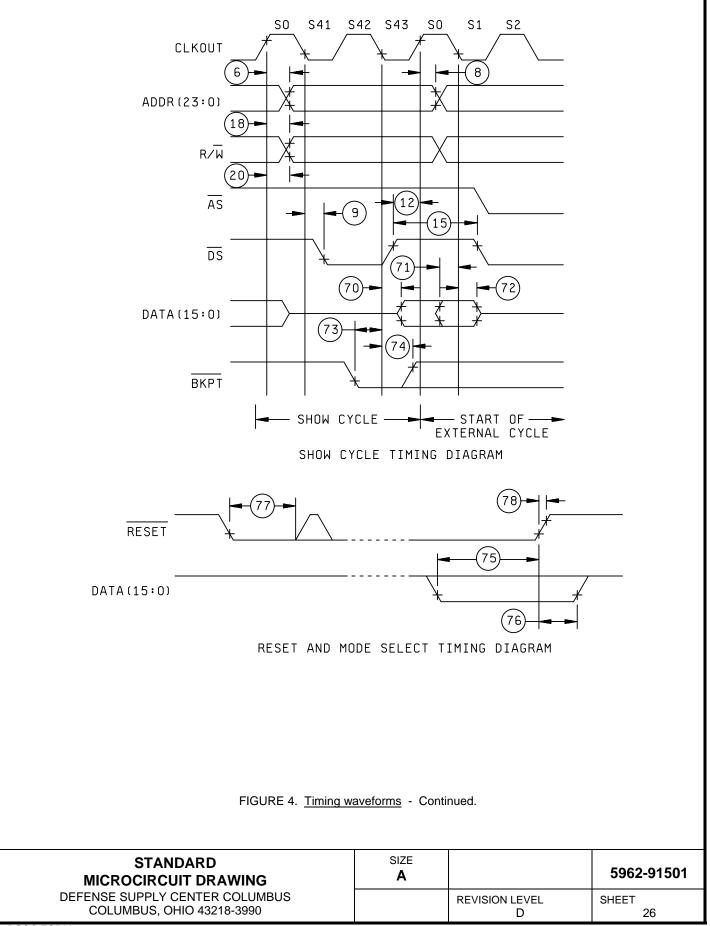

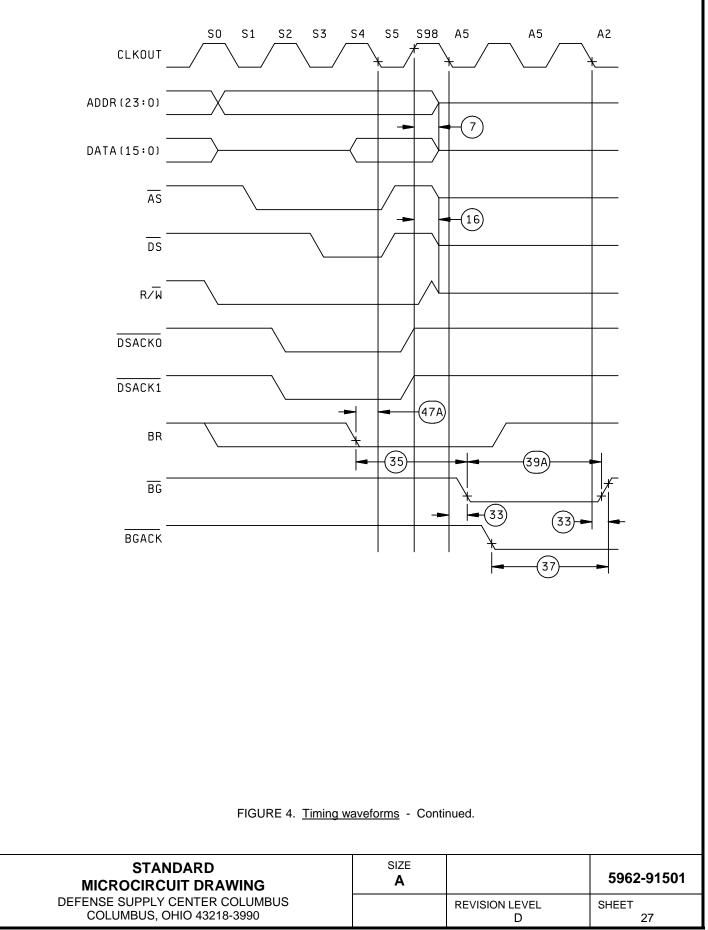

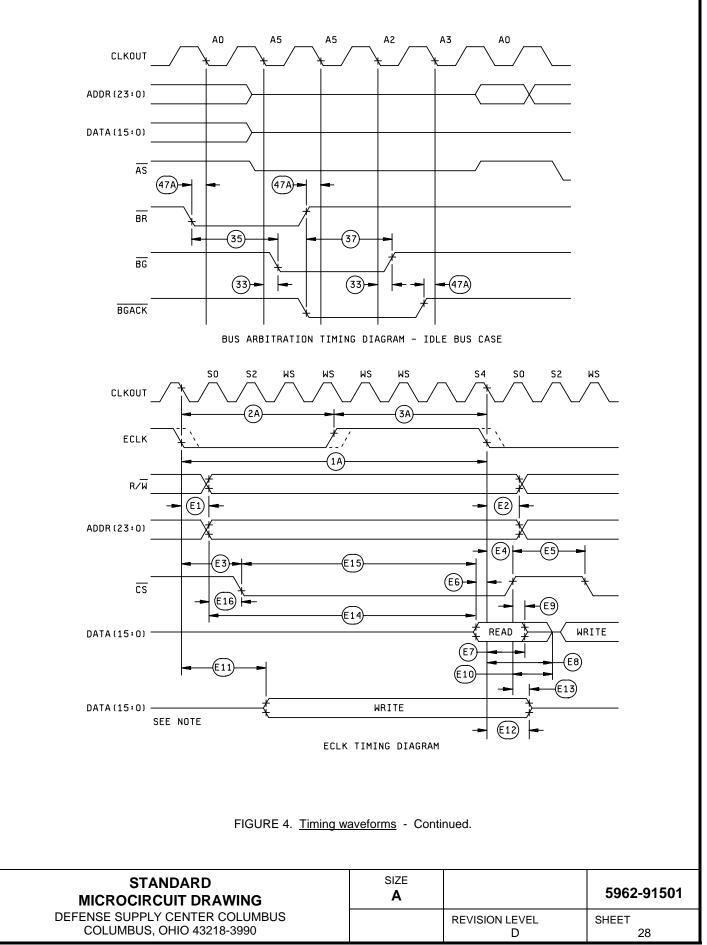

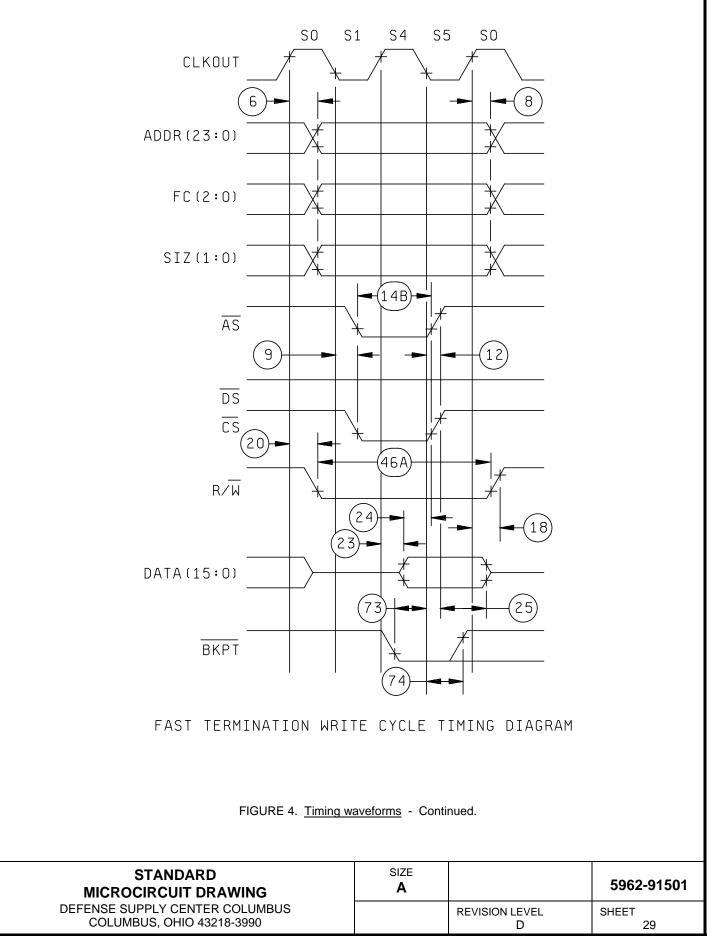

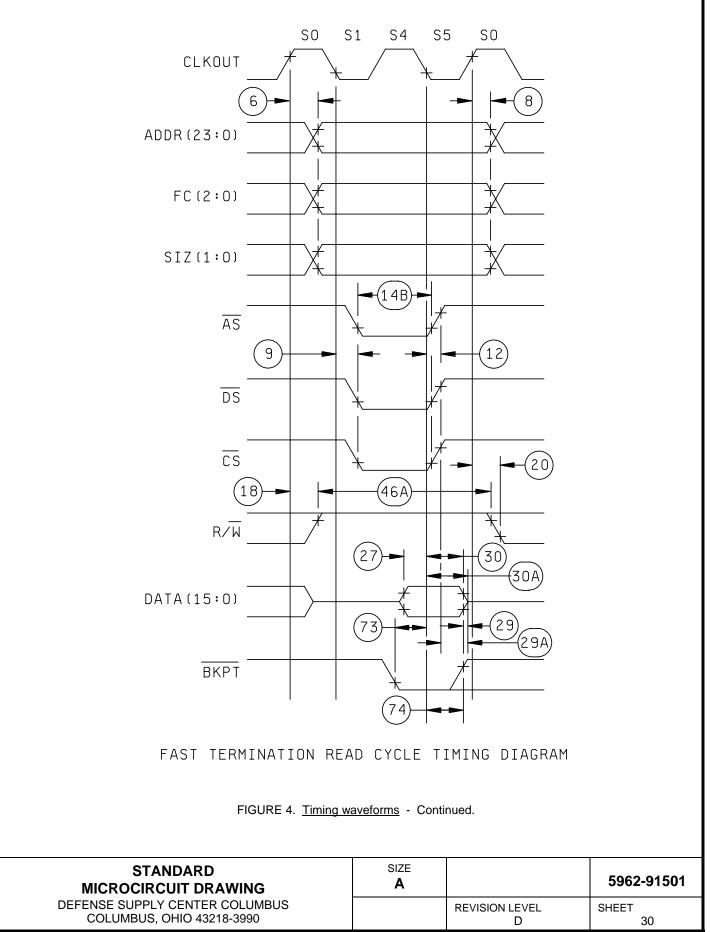

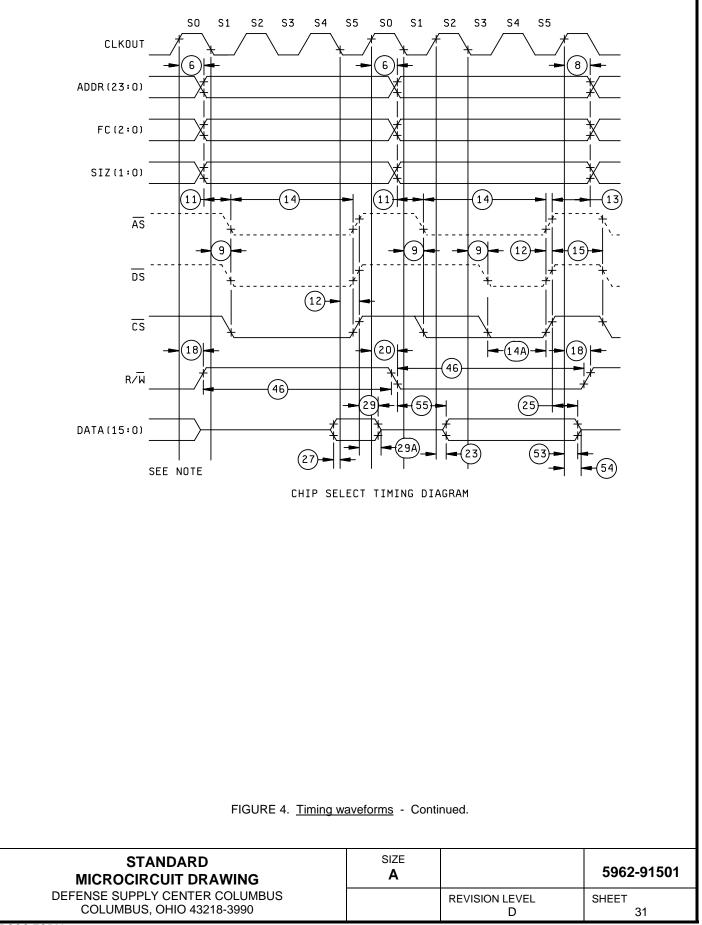

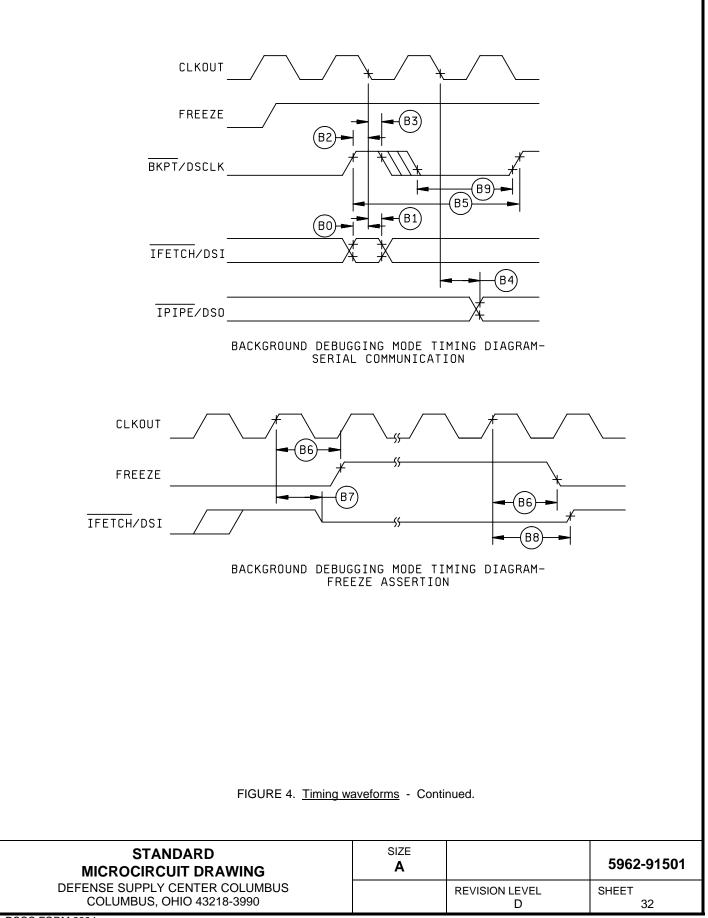

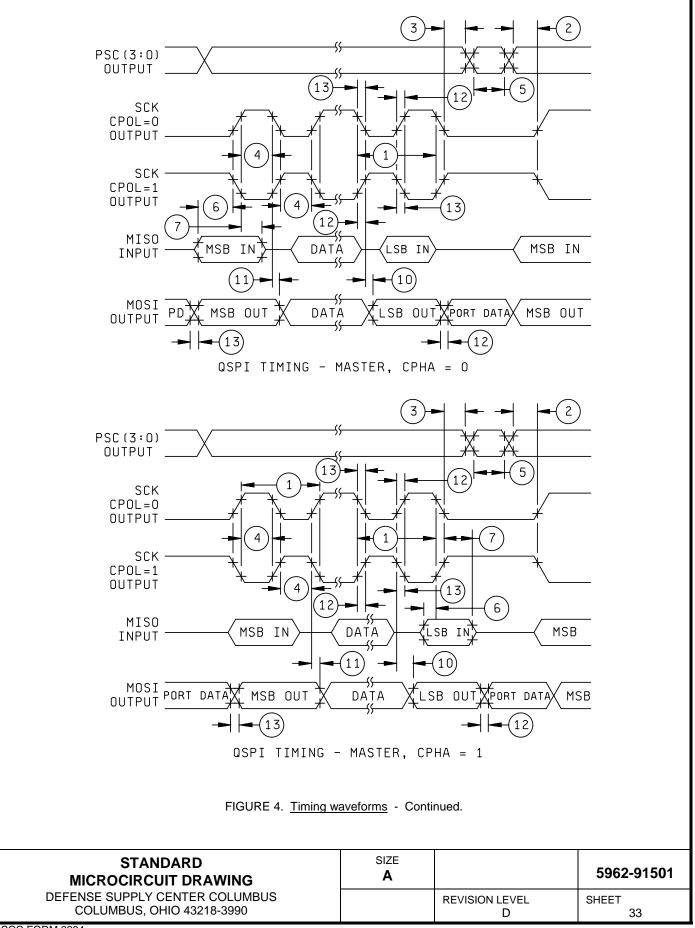

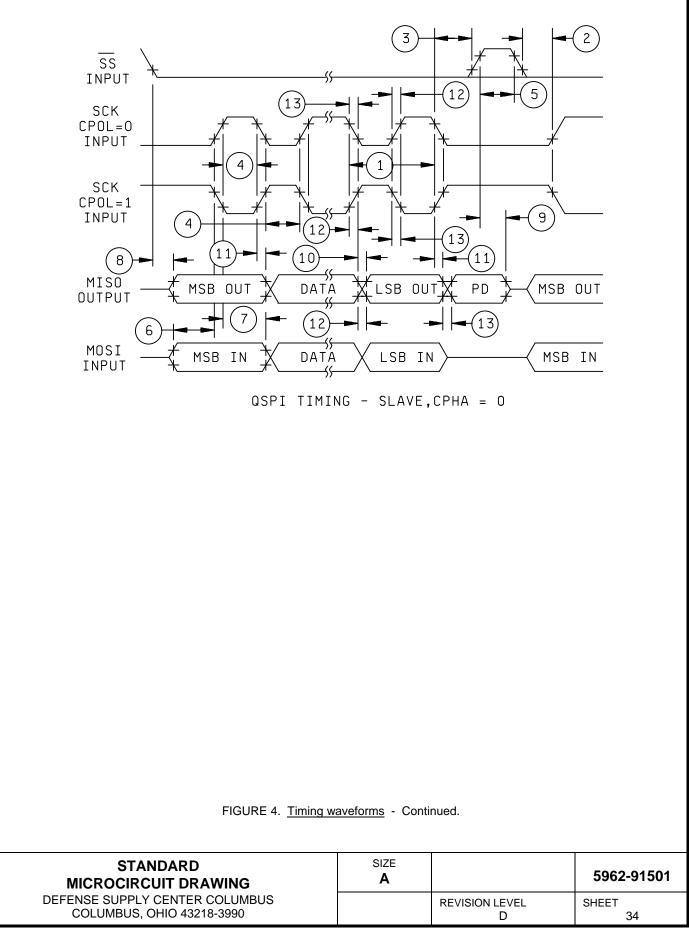

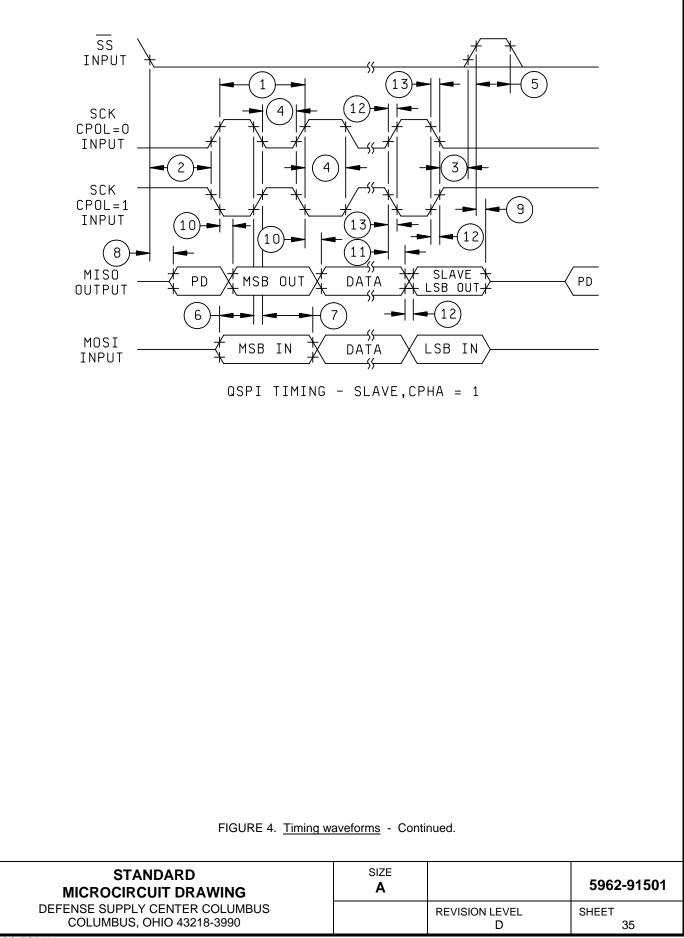

3.2.4 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 4.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-91501 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>D | SHEET 4    |

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change that affects this drawing.

3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-PRF-38535, appendix A).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91501 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | D              | 5          |

|                                                                                                  |                    | TABLE I. <u>Electrical per</u>                                                                                                                                                | formance       | characteris          | <u>tics</u> .    |                          |                       |      |

|--------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|------------------|--------------------------|-----------------------|------|

| Test                                                                                             | Symbol             | $\begin{array}{c} \mbox{Conditions} & \underline{1}\\ -55^{\circ}\mbox{C} \leq T_{C} \leq +129\\ \mbox{unless otherwise spe}\\ \mbox{4.5 V} \leq V_{DD} \leq 5.5 \end{array}$ | 5°C<br>ecified | Group A<br>subgroups | Device<br>type   | Lin                      | nits                  | Unit |

|                                                                                                  |                    |                                                                                                                                                                               |                |                      |                  | Min                      | Max                   |      |

| Input high voltage                                                                               | V <sub>IH</sub>    |                                                                                                                                                                               |                | 1, 2, 3              | All              | 0.7(V <sub>DD</sub> )    | V <sub>DD</sub> + 0.3 | V    |

| Input low voltage                                                                                | V <sub>IL</sub>    |                                                                                                                                                                               |                |                      |                  | V <sub>SS</sub> –<br>0.3 | 0.2(V <sub>DD</sub> ) | V    |

| Input hysteresis 2/                                                                              | V <sub>HYS</sub>   |                                                                                                                                                                               |                |                      |                  | 0.5                      |                       | V    |

| Input leakage current,<br>input-only pins <u>3</u> /                                             | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ or $V_{SS}$<br>Input-only pins.                                                                                                                             |                |                      |                  | -2.5                     | +2.5                  | μΑ   |

| High impedance (off-state)<br>leakage current, all<br>input/output and output<br>pins <u>3</u> / | I <sub>oz</sub>    | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub><br>All input/output and<br>output pins.                                                                                  |                |                      |                  | -2.5                     | +2.5                  | μΑ   |

| CMOS outputs high voltage                                                                        | V <sub>он</sub>    | I <sub>OH</sub> = -10.0 μA<br>Group 1, 2, 4 I/O pins<br>all output pins.                                                                                                      | and            |                      |                  | V <sub>DD</sub> –<br>0.2 |                       | V    |

| CMOS outputs low voltage <u>3</u> /                                                              | V <sub>OL</sub>    | I <sub>OL</sub> = 10.0 μA<br>Group 1, 2, 4 I/O pins<br>all output pins.                                                                                                       | and            |                      |                  |                          | 0.2                   | V    |

| Output high voltage <u>3</u> / <u>4</u> /                                                        | V <sub>он</sub>    | I <sub>OH</sub> = -0.8 mA<br>Group 1, 2, 4 I/O pins<br>all output pins.                                                                                                       | and            |                      |                  | V <sub>DD</sub> –<br>0.8 |                       | V    |

| Output low voltage <u>3</u> /                                                                    | V <sub>OL</sub>    | I <sub>OL</sub> = 1.6mA, Group 1<br>CLKOUT, FREEZE/<br>IPIPE                                                                                                                  | QOUT,          |                      |                  |                          | 0.4                   | V    |

|                                                                                                  |                    | $I_{OL} = 5.3 \text{ mA, Group } 2$<br>I/O pins, CSBOOT,                                                                                                                      |                |                      |                  |                          | 0.4                   |      |

|                                                                                                  |                    | I <sub>OL</sub> = 12 mA, Group 3                                                                                                                                              |                |                      |                  |                          | 0.4                   |      |

| Three-state control input<br>high voltage                                                        | V <sub>IHTSC</sub> |                                                                                                                                                                               |                |                      |                  | 1.6(V <sub>DD</sub> )    | 9.1                   | V    |

| Data bus mode select<br>pull-current <u>5</u> /                                                  | I <sub>MSP</sub>   | $\frac{V_{IN} = V_{IL} \text{ Data}(15:0)}{V_{IN} = V_{IH} \text{ Data}(15:0)}$                                                                                               |                |                      |                  | -15                      | -120                  | μA   |

| VDD supply current,<br>RUN <u>6</u> / <u>7</u> /                                                 | I <sub>DD</sub>    |                                                                                                                                                                               |                |                      | 01<br>02         |                          | 124<br>160            | mA   |

| LPSTOP = 32.768 kHz<br>crystal VCO off<br>(STSIM = 0)                                            | S <sub>IDD</sub>   |                                                                                                                                                                               |                |                      | All              |                          | 350                   | μΑ   |

| LPSTOP (external clock<br>input freq. = max. f <sub>SYS</sub> )                                  | S <sub>IDD</sub>   |                                                                                                                                                                               |                |                      |                  |                          | 5                     | mA   |

| See footnotes at end of table                                                                    |                    |                                                                                                                                                                               |                |                      |                  |                          |                       |      |

| MICROCIRC                                                                                        |                    |                                                                                                                                                                               | siz<br>A       |                      |                  |                          | 5962-9                | 1501 |

| DEFENSE SUPPLY<br>COLUMBUS, C                                                                    |                    |                                                                                                                                                                               |                | RI                   | EVISION LEV<br>D | EL                       | SHEET<br>6            |      |

|                                                           | TABLE              | I. Electrical performance ch                          | aracteristics -    | Continued.        |            |        |       |

|-----------------------------------------------------------|--------------------|-------------------------------------------------------|--------------------|-------------------|------------|--------|-------|

| Test                                                      | Symbol             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ | Group /<br>subgrou |                   | Lir        | nits   | Unit  |

|                                                           |                    |                                                       |                    |                   | Min        | Max    |       |

| Clock synthesizer                                         | V <sub>DDSYN</sub> |                                                       | 1, 2, 3            | 01                | 4.5        | 5.5    | V     |

| operating voltage                                         |                    | -                                                     |                    | 02                | 4.75       | 5.25   |       |

| V <sub>DDSYN</sub> supply current,<br>32.768 kHz crystal, | I <sub>DDSYN</sub> |                                                       |                    | 01                |            | 1      | mA    |

| VCO on, max. f <sub>SYS</sub> <u>6</u> /                  |                    | -                                                     |                    | 02                |            | 2      |       |

| External clock, max. $f_{SYS}$                            | IDDSYN             |                                                       |                    | 01                |            | 5<br>6 | mA    |

| LPSTOP, 32.768 kHz<br>crystal, VCO off<br>(STSIM = 0)     | SIDDSYN            |                                                       |                    | All               |            | 150    | μΑ    |